### Remarks on Memory (Applies to GPUs and CPUs)

- In our dot product kernel, we could have done everything in global memory, but ...

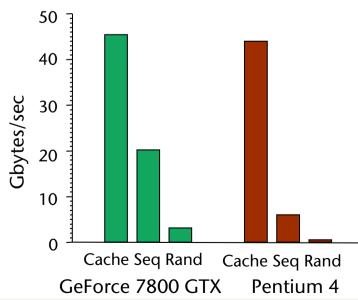

- Global memory bandwidth is sloooow:

Ideal Reality

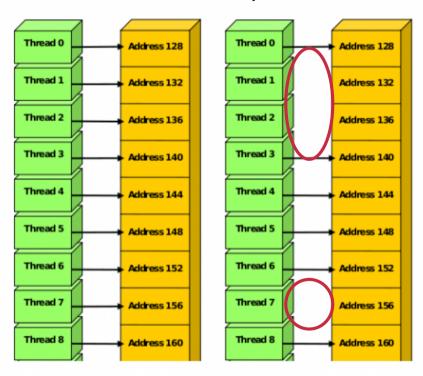

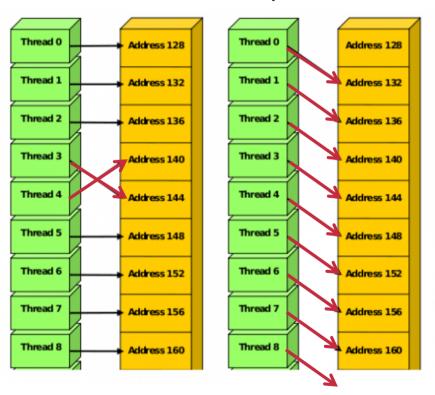

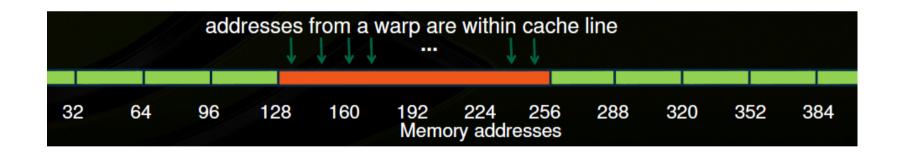

### **Coalesced Memory Access**

One of the most important optimization techniques for massively parallel algorithm design (on GPUs and — to some degree — CPUs!)

#### Coalesced memory accesses

#### **Uncoalesced** memory accesses

- When does the GPU win over the CPU?

- Arithmetic intensity of an algorithm :=  $\frac{\text{number of arithmetic operations}}{\text{amount of transferred bytes}}$

- Sometimes also called computational intensity

- Unfortunately, many (most?) algorithms have a low arithmetic intensity → they are bandwidth limited

- GPU wins if memory access is "streamed" = coalesced

- Hence, "stream programming architecture"

SS

#### **How to Achieve Coalesced Access**

- Addresses from a warp ("thread-vector") are converted into memory line requests

- Line sizes: 32B (= 32x char) and 128B (= 32x float)

- Goal is to maximally utilize the bytes in these lines

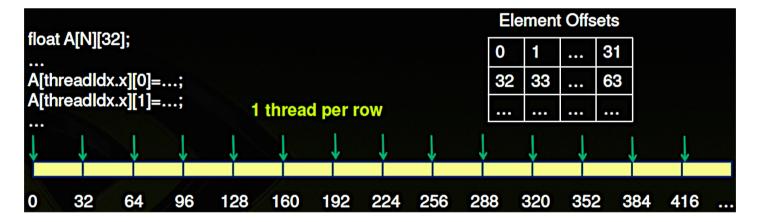

### 2D Array Access Pattern (row major)

Consider the following code piece in a kernel (e.g., matrix × vector):

```

for ( int j = 0; j < 32; j ++ ) {

float x = A[treadIdx.x][j];

... do something with it ...</pre>

```

- ➤ Uncoalesced access pattern:

- Elements read on 1<sup>st</sup> SIMT access: 0, 32, 64, ...

- Elements read on 2<sup>nd</sup> SIMT access: 1, 33, 65, ...

- Also, extra data will be transferred in order to fill the cache line size

- Generally, most natural access pattern for direct port of a C/C++ code!

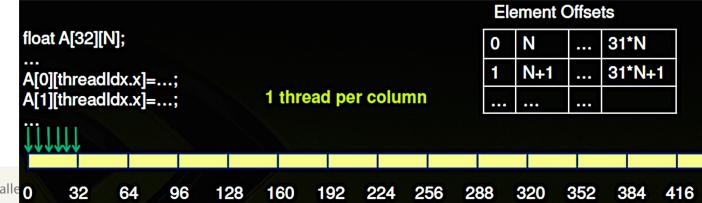

#### Transposed 2D Array Access Pattern

- This "natural" way to store matrices is called row major order

- Column major := store a logical row in a physical column

```

• I.e., A_{00} \to A[0][0], A_{01} \to A[1][0], A_{02} \to A[2][0], ...

A_{10} \rightarrow A[0][1], A_{11} \rightarrow A[1][1], A_{12} \rightarrow A[2][1], ...

A_{20} \to A[0][2] \dots

```

Transform the code piece (e.g., rowxcolumn) to column major:

```

for ( int j = 0; j < 32; j ++ ){

float x = A[j][treadIdx.x];

... do something with it ...

```

- Now, we have coalesced accesses:

- Elements read on 1st SIMT access: 0, 1, 2, ..., 31

- Elements read on 2<sup>nd</sup> SIMT access: 32, 33, ..., 63

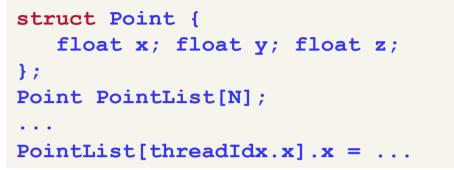

## Array of Structure or Structure of Array?

• An array of structures (AoS) behaves like row major accesses:

A structure of arrays (SoA) behaves like column major access:

```

struct PointList {

float x[N];

float y[N];

float z[N];

};

...

PointList.x[threadIdx.x] = ...

```

## Simulating Heat Transfer in Solid Bodies

- Assumptions:

- For sake of illustration, our domain is 2D

- Discretize domain → 2D grid (common approach in simulation)

- A few designated cells are "heat sources"

→ cells with constant temperature

Simulation model (simplistic):

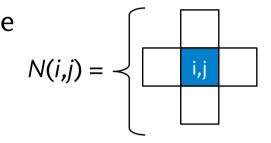

$$T_{i,j}^{n+1} = T_{i,j}^n + \sum_{(k,l)\in N(i,j)} \mu(T_{k,l}^n - T_{i,j}^n)$$

$$\Leftrightarrow T_{i,j}^{n+1} = (1 - N\mu)T_{i,j}^n + \mu \sum_{(k,l) \in N(i,j)} T_{k,l}^n$$

(1)

May 2014

N = number of cells in the neighborhood

Iterate this (e.g., until convergence to steady-state)

- Do we achieve energy conservation?

- For sake of simplicity, assume

- Energy consumption iff  $\sum_{i,j} T_{i,j}^{n+1} \stackrel{!}{=} \sum_{i,j} T_{i,j}^{n}$  (2)

- Plugging (1) into (2) yields

$$(1 - N\mu) \sum_{i,j} T_{i,j}^n + \mu \sum_{i,j} \sum_{(k,l) \in N(i,j)} T_{k,l}^n \stackrel{!}{=} \sum_{i,j} T_{i,j}^n$$

• Therefore,  $\mu$  is indeed a free material parameter (= "heat flow speed")

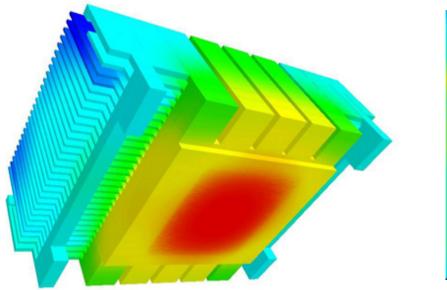

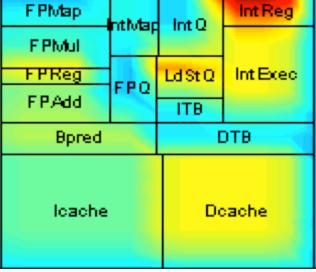

Example: heat simulation of ICs and cooling elements

### MassPar Algorithm Design Pattern: Double Buffering

- Observations:

- Each cell's next state can be computed completely independently

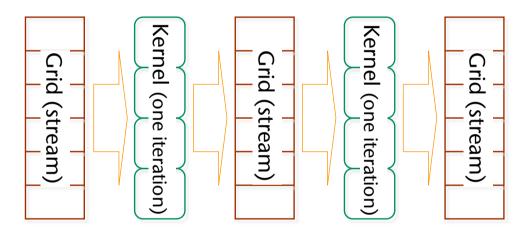

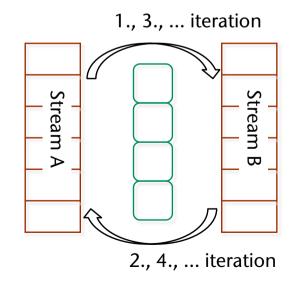

- > We can arrange our computations like this:

General parallel programming pattern: double buffering ("ping pong")

#### Algorithm

- One thread per cell

- 1. Kernel for resetting heat sources:

```

if ( cell is heat cell ):

read temperature from constant "heating stencil"

```

2. Kernel for one transfer step:

```

Read all neighbor cells: input_grid[tid.x+-1][tid.y+-1]

Accumulate them

Write new temperature in output_grid[tid.x][tid.y]

```

- 3. Swap pointers to input & output grid (done on host)

- Challenge: border cells! (very frequent problem in sim. codes)

- Use if-then-else in above kernel?

- Use extra kernel that is run only for border cells?

- Introduce padding around domain? Arrange domain as torus?

# Texture Memory Optional

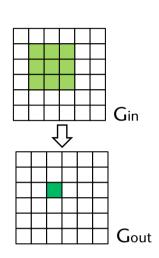

- Many computations have the following characteristics:

- They iterate a simple function many times

- They work on a 2D/3D grid

- We can run one thread per grid cell

- Each thread only needs to look at neighbor cells

- Each iteration transforms an input grid into an output grid

- For this kind of algorithms, there is texture memory:

- Special cache with optimization for spatial locality

- Access to neighbor cells is very fast

- Important: can handle out-of-border accesses automatically by clamping or wrap-around!

- For the technical details: see "Cuda by Example",

Nvidia's "CUDA C Programming Guide",

# **Optional**

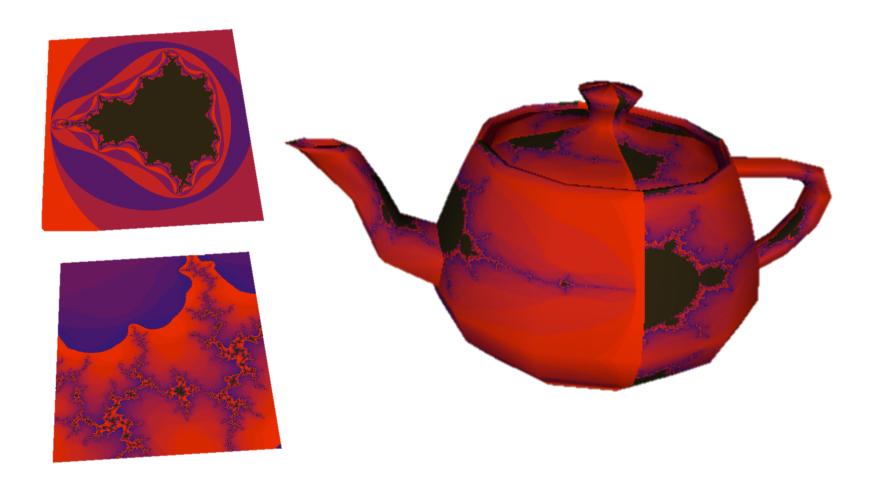

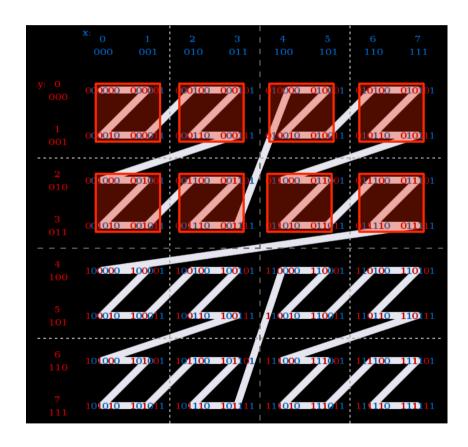

The locality-preserving cache is probably achieved by arranging data via a space-filling curve:

# Optional

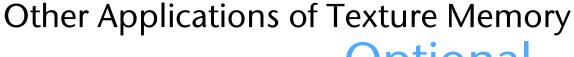

- Most image processing algorithms exhibit this kind of locality

- Trivial example: image addition / subtraction → neighboring threads access neighboring pixels

SS

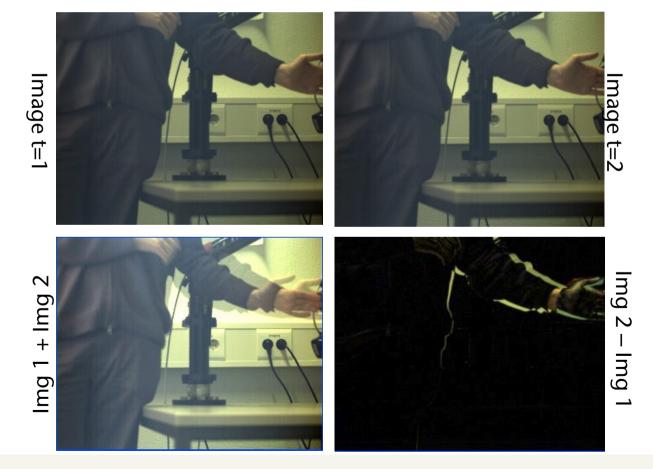

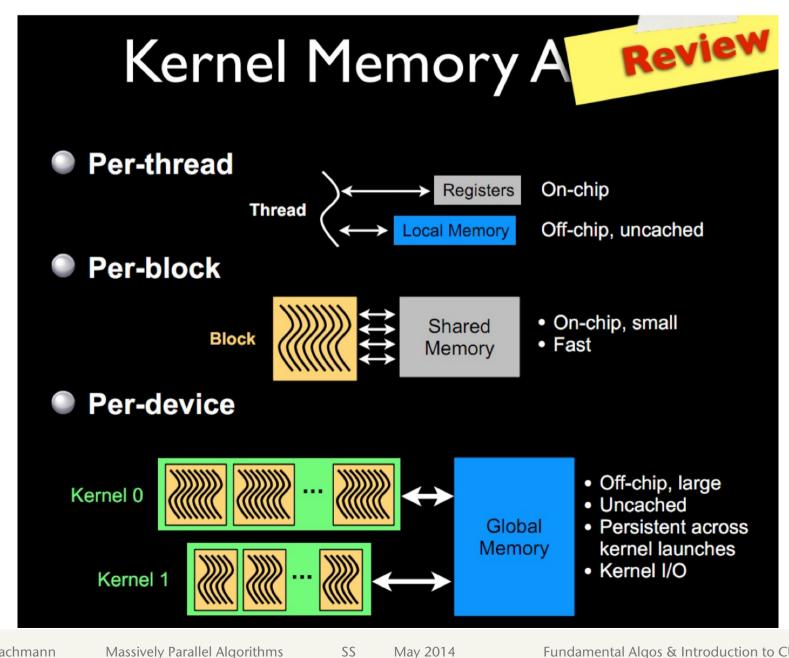

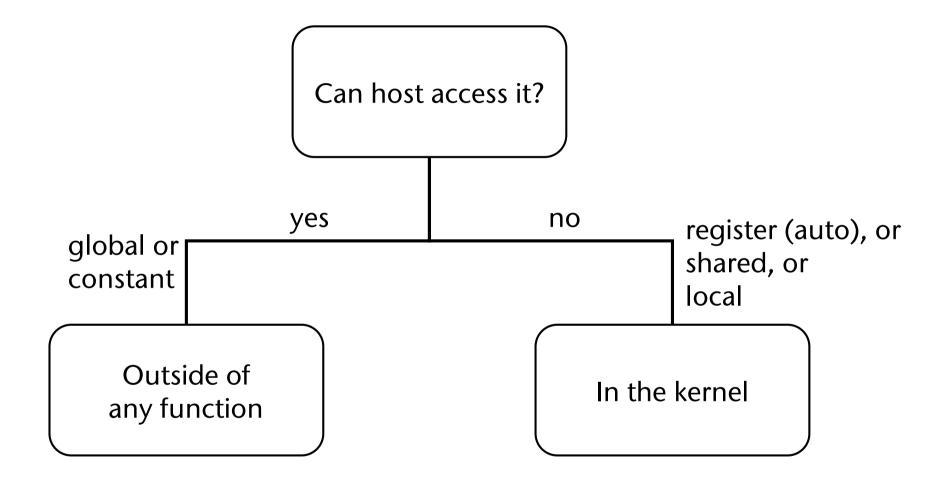

### **CUDA's Memory Hierarchy**

## **CUDA Variable Type Qualifiers**

| Variable declaration |          |                           | Memory   | Access | Lifetime    |

|----------------------|----------|---------------------------|----------|--------|-------------|

| device               | local    | <pre>int LocalVar;</pre>  | local    | thread | thread      |

| device               | shared   | <pre>int SharedVar;</pre> | shared   | block  | block       |

| device               |          | <pre>int GlobalVar;</pre> | global   | grid   | application |

| device               | constant | int ConstantVar;          | constant | grid   | application |

#### Remarks:

- \_\_device\_\_ is optional when used with \_\_local\_\_, \_\_shared\_\_, or \_\_constant\_

- Automatic variables without any qualifier reside in a register

- Except arrays, which reside in local memory (slow)

### **CUDA Variable Type Performance**

| Vari      | able declaration              | Memory   | Penalty |

|-----------|-------------------------------|----------|---------|

|           | <pre>int var;</pre>           | register | 1x      |

|           | <pre>int array_var[10];</pre> | local    | 100x    |

| shared    | <pre>int shared_var;</pre>    | shared   | 1x      |

| device    | <pre>int global_var;</pre>    | global   | 100x    |

| constant_ | _ int constant_var;           | constant | 1x      |

- Scalar variables reside in fast, on-chip registers

- Shared variables reside in fast, on-chip memories

- Thread-local arrays & global variables reside in uncached off-chip memory

May 2014

Constant variables reside in cached off-chip memory

#### Where to Declare Variables?

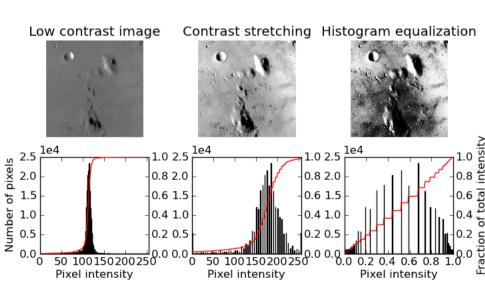

## Massively Parallel Histogramm Computation

Definition (for images):

$$h(x) = \#$$

pixels with level  $x$

$$x \in 0, \ldots, L-1$$

$L = \#$  levels

$$L = \#$$

levels

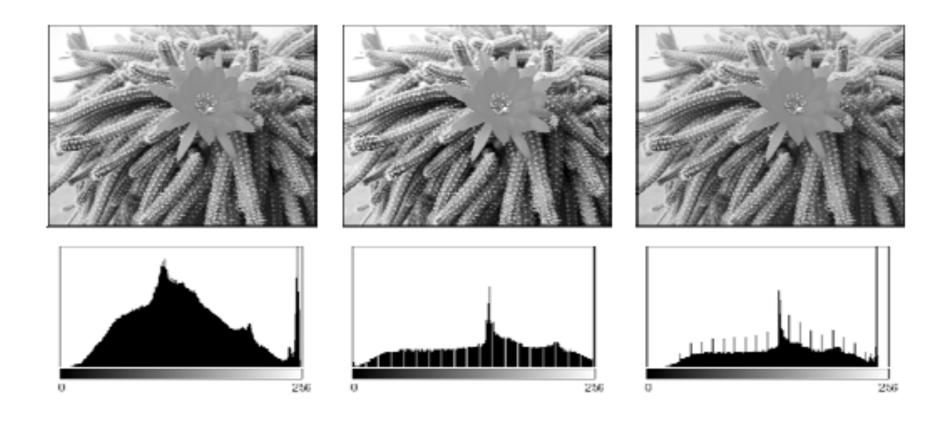

- Applications: many!

- Huffman compression (see computer science 2<sup>nd</sup> semester)

- Histogram equalization (see Advanced Computer Graphics)

Vumber of students

Score achieved in exam

#### The sequential algorithm:

```

unsigned char input[MAX_INP_SIZE];// e.g. image

// # valid chars in input

int input size;

// clear histogram

for (int i = 0; i < 256; i ++ )

histogram[i] = 0;

for (int i = 0; i < input size; i ++ )</pre>

histogram[ input[i] ] ++ ;  // real histogram comput.

// verify histogram

long int total count = 0;

for (int i = 0; i < 256; i ++ )

total count += histogram[i];

if ( total count != input size )

fprintf(stderr, "Error! ...");

```

- Naïve "massively parallel" algorithm:

- One thread per bin (e.g., 256)

- Each thread scans the complete input and counts the number of occurrences of its "own" intensity level in the image

- At the end, each thread stores its level count in its histogram slot

- Disadvantage: not so massively parallel ...

- New approach: "one thread per pixel"

- The setup on the host side:

#### Notes:

- Letting **threadsPerBlock** = 256 makes things much easier in our case

- Letting nBlocks = (number of multiprocessors [SMs] on the device) \* 2 is a good rule of thumb, YMMV

- On current hardware (Kepler) → ~ 16384 threads

The kernel on the device side:

Problem: race condition!!

#### **Solution: Atomic Operations**

The kernel with atomic add:

Prototype of atomicAdd():

```

T atomicAdd( T * address, T val )

```

where **T** can be **int**, **float** (and a few other types)

- Semantics: while atomicAdd performs its operation on address, no other thread can access this memory location! (neither read, nor write)

- Problem: this algorithm is much slower than the sequential one!

- Lesson: always measure performance against CPU!

- Cause: congestion

- Lots of threads waiting for a few memory locations to become available

Remedy: partial histograms in shared memory

```

computeHistogram( unsigned char * input,

long int input size,

unsigned int histogram[256] )

shared unsigned int partial histo[256];

partial histo[ threadIdx.x ] = 0;

syncthreads();

int i = threadIdx.x + blockIdx.x * blockDim.x;

int stride = blockDim.x * gridDim.x;

while ( i < input size ) {</pre>

atomicAdd( & partial histo[input[i]], 1 );

i += stride;

syncthreads();

atomicAdd( & histogram[threadIdx.x],

partial histo[threadIdx.x] );

```

Note: now it's obvious why we chose 256 threads/block

### More Atomic Operations

- All programming languages / libraries / environments providing for some kind of parallelism/concurrency have one or more of the following atomic operations:

- int atomicExch( int\* address, int val ):

Read old value at address, store val in address, return old value

- Atomic AND: performs the following in one atomic operation

```

int atomicAnd( int* address, int val )

{

int old = *address;

*address = old & val;

return old;

}

```

- Atomic Minimum operation (just analogous to AND)

- Atomic compare-and-swap (CAS), and several more ...

- The fundamental atomic operation Compare-And-Swap:

- In CUDA: int atomicCAS(int\* address, int compare, int val)

- Performs this little algorithm atomically:

```

atomic_compare_and_swap( address, compare, new_val ):

old ← value in memory location address

if compare == old:

store new_val → memory location address

return old

```

Theorem (w/o proof):

All other atomic operations can be implemented using atomic compare-and-swap.

# **Optional**

#### Example:

# **Image Restoration Using Histograms**

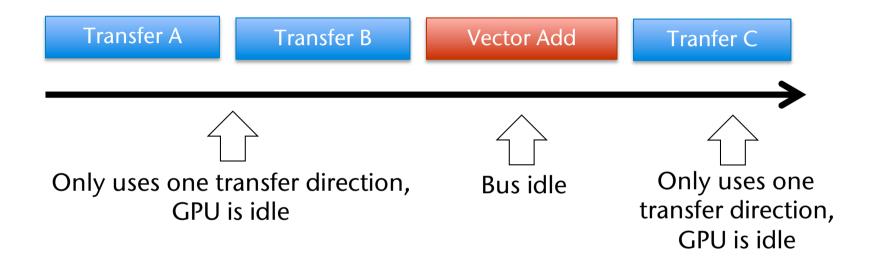

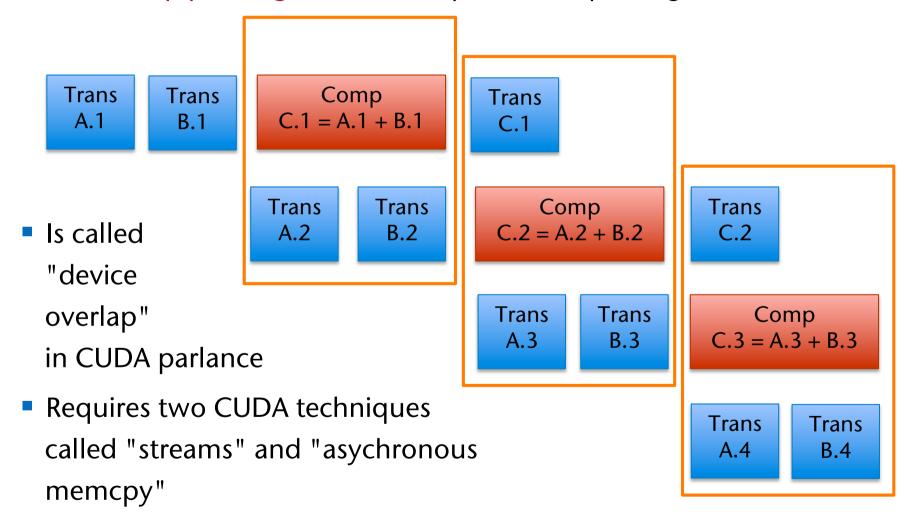

#### Advanced GPU & Bus Utilization

■ Problem with performance, if lots of transfer between GPU

CPU:

Solution: pipelining (the "other" parallelism paradigm)

#### For More Information on CUDA ...

- CUDA C Programming Guide (zur Programmiersprache)

- CUDA C Best Practices Guide (zur Performance-Steigerung)

- /Developer/NVIDIA/CUDA-5.0/doc/html/index.html (zum Runtime API)

### Concepts we Have Not Covered Here

- Dynamic parallelism (threads can launch new threads)

- Good for irregular data parallelism (e.g., tree traversal, multi-grids)

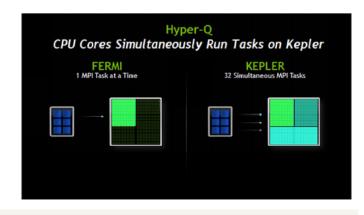

- Running several tasks at the same time on a GPU (via MPI; they call it "Hyper-Q")

#### See:

- "Introduction to CUDA 5.0" on the course web page

- "CUDA C Programming Guide" at docs.nvidia.com/cuda/index.html

- Graphics Interoperability:

- Transfer images directly from CUDA memory to OpenGL's framebuffer

- Dynamic shared memory

- Dynamic memory allocation in the kernel

- Can have serious performance issues

- Pinned CPU memory (

- CUDA Streams

- Multi-GPU programming, GPU-to-GPU memory transfer

- Zero-copy data transfer

- Libraries: CUBLAS, Thrust, ...

- Voting functions ( \_\_all(), \_\_any() )

With Graphics Interoperability, you can render results from CUDA directly in a 3D scene, e.g. by using them as textures